Employees of the MTS Department took part in the seminar “Improve RTL verification productivity by connecting to MATLAB and Simulink”

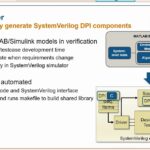

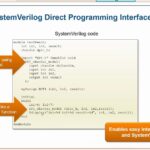

RTL validation remains a major issue in FPGA and ASIC design projects. This session demonstrated how engineers from different industries can work together in MATLAB / Simulink to increase efficiency and reduce verification time.

The main reasons influencing the efficiency and increase of the inspection time were discussed. It demonstrates how MATLAB and Simulink can help optimize validation time in different ways, and shows how some of our key users use these new techniques to provide verification phases at the earliest stage of project development.